# SCHOOL OF COMPUTATION, INFORMATION AND TECHNOLOGY — INFORMATICS

TECHNISCHE UNIVERSITÄT MÜNCHEN

Master's Thesis in Informatics

# Hardware-Assisted Memory Safety for WebAssembly

Martin Fink

# SCHOOL OF COMPUTATION, INFORMATION AND TECHNOLOGY — **INFORMATICS**

TECHNISCHE UNIVERSITÄT MÜNCHEN

Master's Thesis in Informatics

# **Hardware-Assisted Memory Safety for** WebAssembly

# Hardwaregestützte Speichersicherheit für WebAssembly

Author: Martin Fink

Prof. Pramod Bhatotia Supervisor: Advisor: Dimitrios Stavrakakis

Submission Date: 15.04.2024

| I confirm that this master's thesis is my own wo and material used. | ork and I have documented all sources |

|---------------------------------------------------------------------|---------------------------------------|

|                                                                     |                                       |

| Munich, 15.04.2024                                                  | Martin Fink                           |

|                                                                     |                                       |

|                                                                     |                                       |

|                                                                     |                                       |

# Acknowledgments

First and foremost, I would like to thank my supervisor, Pramod Bhatotia. My academic life would have been quite different without his guidance and support. Since writing my Bachelor's thesis in 2021, his chair has been a welcoming place, allowing me to grow personally and as a researcher while opening many doors for the future. I am also very grateful to my advisor, Dimitrios Stavrakakis, for answering my questions about memory safety, giving me feedback on my work, and helping me debug weird measurements. Thanks to Dennis Sprokholt for his feedback on my formalizations.

To my friends, who have been with me throughout my master's thesis and beyond in both academic and personal journeys: Thank you for making this time enjoyable. While I cannot name everyone here, I want to extend special thanks to Andreas and Christoph for their feedback on this thesis.

During my last semester break, I had the opportunity to do an internship at Huawei's Helsinki System Security Lab. I gained extensive knowledge in compilers, WebAssembly, and security, greatly enhanced by the collaboration with my colleagues Antti, Janne, Carlos, Rémi, Valentin, and my manager, Jan-Erik, despite our short time sharing the office.

Lastly, I'd like to thank my family. Their support enabled me to study in Munich, and I am forever thankful for the unconditional support they have provided me.

# **Abstract**

In this thesis, we investigate the design and implementation of an extension to WebAssembly (WASM) aiming to prevent the issue of memory safety vulnerabilities, particularly in languages like C and C++ that compile to WASM. Despite WASM's sandboxing feature that isolates applications from other instances and the host, these languages are still prone to memory safety bugs due to their lack of memory safety provided by the type system or prevalent libraries. This thesis introduces a minimally invasive extension to WASM designed to allow implementations to utilize diverse hardware- or software-based memory safety mechanisms.

Our work includes a complete compiler toolchain for C/C++ in LLVM, hardening programs, and providing spatial and temporal memory safety for heap and stack allocations. We showcase an implementation utilizing ARM's hardware-based Memory Tagging Extension (MTE), that offers a high-performance, low-overhead solution for spatial and temporal memory safety issues and is compatible with real-world performance requirements.

We further explore the possibility of integrating MTE into WASM's sandboxing mechanism, improving the performance of programs relying on expensive software-based bounds checks. The empirical evaluation on actual hardware platforms validates our proposed system's practicality and performance advantages.

Our work enhances WebAssembly with memory safety guarantees by introducing a generic, minimally invasive extension with low overhead. It sets a groundwork for further studies, suggesting directions for improving compatibility, optimizing performance, and incorporating various memory safety mechanisms.

# Zusammenfassung

In dieser Arbeit untersuchen wir den Entwurf und die Implementierung einer Erweiterung von WebAssembly (WASM), die darauf abzielt, das Problem der Speichersicherheitsschwachstellen zu verhindern, insbesondere in Sprachen wie C und C++, die nach WASM kompiliert werden. Trotz der Sandboxing-Funktion von WASM, die Anwendungen von anderen Instanzen und dem Host isoliert, sind diese Sprachen immer noch anfällig für Speichersicherheitsfehler, da sie keine Speichersicherheit durch das Typsystem oder gängige Bibliotheken bieten. In dieser Arbeit wird eine minimal invasive Erweiterung von WASM vorgestellt, die es Implementierungen ermöglicht, verschiedene hardware- oder softwarebasierte Speichersicherheitsmechanismen zu nutzen.

Unsere Arbeit umfasst eine vollständige Compiler-Toolchain für C/C++ in LLVM, die Härtung von Programmen und die Bereitstellung von räumlicher und zeitlicher Speichersicherheit für Heap- und Stack-Allokationen. Wir stellen eine Implementierung vor, die ARMs hardwarebasiertes Memory Tagging Extension (MTE) verwendet, das eine leistungsstarke Lösung mit geringem Aufwand für räumliche und zeitliche Speichersicherheit bietet und mit realen Leistungsanforderungen kompatibel ist.

Außerdem untersuchen wir die Möglichkeit, MTE in den Sandboxing-Mechanismus von WASM zu integrieren, um die Leistung von Programmen zu verbessern, die auf teure softwarebasierte Bound Checks angewiesen sind. Die empirische Evaluierung auf aktuellen Hardware-Plattformen bestätigt die Praktikabilität und die Leistungsvorteile des von uns vorgeschlagenen Systems.

Unsere Arbeit erweitert WebAssembly um Garantien für Speichersicherheit, indem wir eine generische, minimal invasive Erweiterung mit geringem Overhead einführen. Sie bildet die Grundlage für weitere Studien und zeigt Wege zur Verbesserung der Kompatibilität, zur Optimierung der Leistung und zur Integration verschiedener Speichersicherheitsmechanismen auf.

# **Contents**

| A  | knov   | vledgm  | ients                                   | iii |

|----|--------|---------|-----------------------------------------|-----|

| Αl | ostrac | :t      |                                         | iv  |

| Zι | ısamı  | nenfas  | sung                                    | v   |

| 1. | Intro  | oductio | n                                       | 1   |

| 2. | Back   | cgroun  | d                                       | 3   |

|    |        | _       | ssembly                                 | 3   |

|    |        | 2.1.1.  | WebAssembly Sandbox                     | 4   |

|    | 2.2.   | Memo    | ry Safety in the context of WebAssembly | 4   |

|    |        | 2.2.1.  | Software-Based Mitigations              | 5   |

|    | 2.3.   | Memo    | ry Safety Hardware Extensions           | 6   |

|    |        | 2.3.1.  | Memory Tagging Extension (MTE)          | 7   |

|    |        | 2.3.2.  | Pointer Authentication (PAC)            | 7   |

| 3. | Mot    | ivation |                                         | 9   |

| 4. | Ove    | rview   |                                         | 11  |

| 5. | Desi   | ign     |                                         | 13  |

|    | 5.1.   | Threat  | Model                                   | 13  |

|    |        | 5.1.1.  | Internal Memory Safety                  | 14  |

|    |        | 5.1.2.  | External Memory Safety                  | 14  |

|    | 5.2.   | Overv   | iew                                     | 15  |

|    | 5.3.   | WebA    | ssembly Extension                       | 15  |

|    |        | 5.3.1.  | Typing Rules                            | 17  |

|    |        | 5.3.2.  | Small-Step Reduction Rules              | 18  |

|    |        | 5.3.3.  | Example                                 | 19  |

|    |        | 5.3.4.  | Heap Safety                             | 21  |

|    |        | 5.3.5.  | Stack Safety                            | 22  |

|    |        | 5.3.6.  | Example                                 | 22  |

# Contents

| 6. | Imp                      | lement  | ation                                       | <b>2</b> 4 |  |

|----|--------------------------|---------|---------------------------------------------|------------|--|

|    | 6.1.                     | LLVM    | [                                           | 24         |  |

|    |                          | 6.1.1.  | LLVM IR                                     | 24         |  |

|    |                          | 6.1.2.  | LLVM Sanitizer Pass                         | 25         |  |

|    |                          | 6.1.3.  | C extension                                 | 25         |  |

|    | 6.2.                     | WASI    | Libc Modifications                          | 26         |  |

|    | 6.3.                     | Intern  | al Memory Safety                            | 27         |  |

|    |                          | 6.3.1.  | Tagging Memory                              | 28         |  |

|    |                          | 6.3.2.  | Lowering WebAssembly (WASM) to machine code | 28         |  |

|    |                          | 6.3.3.  | Migration of the Linear Memory              | 29         |  |

|    | 6.4.                     | Exterr  | nal Memory Safety                           | 30         |  |

| 7. | Eval                     | uation  |                                             | 34         |  |

|    | 7.1.                     | Experi  | imental Setup                               | 34         |  |

|    | 7.2.                     | Perfor  | mance Overheads                             | 35         |  |

|    | 7.3.                     | Memo    | ory Overheads                               | 36         |  |

|    | 7.4.                     | Securi  | ty Guarantees                               | 37         |  |

|    |                          | 7.4.1.  | External Memory Safety                      | 37         |  |

|    |                          | 7.4.2.  | Internal Memory Safety                      | 37         |  |

|    | 7.5.                     | MTE I   | Performance evaluation                      | 38         |  |

|    |                          | 7.5.1.  | Instruction Latencies and Throughput        | 38         |  |

|    |                          | 7.5.2.  | Tagging Primitives                          | 39         |  |

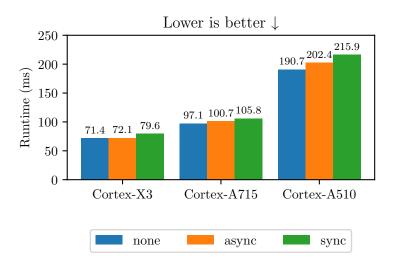

|    |                          | 7.5.3.  | Synchronous and Asynchronous Mode           | 40         |  |

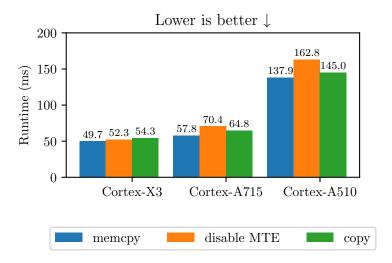

|    |                          | 7.5.4.  | Migrating Tagged Memory                     | 40         |  |

| 8. | Rela                     | ited Wo | ork                                         | 43         |  |

|    | 8.1.                     | Memo    | ory Safety for WebAssembly                  | 43         |  |

|    |                          | 8.1.1.  | MS-WASM                                     | 43         |  |

|    |                          | 8.1.2.  | RichWasm                                    | 43         |  |

|    |                          | 8.1.3.  | Pointer Authentication                      | 44         |  |

|    | 8.2. Memory Safety for C |         |                                             |            |  |

|    |                          |         | Memory-Safe C Language Dialects             | 44         |  |

|    |                          | 8.2.2.  | Instrumentation-Based Memory Safety         | 44         |  |

|    |                          | 8.2.3.  | Hardened Memory Allocators                  | 46         |  |

| 9. | Con                      | clusion | 1                                           | 48         |  |

|    | 9.1.                     | Future  | e Work                                      | 48         |  |

|    |                          | 9.1.1.  | Additional Implementations                  | 48         |  |

|    |                          | 9.1.2.  | Backward Compatibility                      | 49         |  |

# Contents

| 9.1.3.<br>9.1.4.                     | Combining Guard Pages and Memory Tagging Extension (MTE) Pointer Authentication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49<br>49                               |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| A.1.1<br>A.1.2<br>A.2. Runr<br>A.2.1 | ling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50<br>50<br>50<br>51<br>52<br>52<br>52 |

| Abbreviation                         | as a second seco | 53                                     |

| List of Figure                       | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54                                     |

| List of Tables                       | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56                                     |

| Bibliography                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57                                     |

# 1. Introduction

In recent years, WASM [10] has gained prominence [17] as a versatile compilation target, serving not only to web-based applications but also to a broader spectrum of use cases [37]. At its core, WASM is engineered as an efficient compilation target for high-level, compiled languages such as C and C++. A fundamental aspect of its design is its linear memory model, which allows these languages to efficiently compile to WASM and WASM to efficiently compile to various architectures.

While WebAssembly provides a sandbox for untrusted code, which protects the host and other guests from malicious or buggy code, it does not inherently prevent memory safety issues within an application's memory space. This limitation becomes particularly evident when compiling languages like C or C++, where there are no language-level guarantees to prevent these bugs.

Recent ISA extensions, such as ARM's Pointer Authentication (PAC) [25] and Memory Tagging Extension (MTE) [4], offer promising, high-performance solutions by providing building blocks that incur low performance overhead. These hardware extensions are designed to effectively address memory safety concerns.

We introduce an extension to WASM to address spatial and temporal memory safety bugs with a prototype implementation utilizing MTE to efficiently implement the safety guarantees. Our approach requires no modification to the source code, as we provide a complete compiler toolchain and standard library that can be used to harden unmodified C/C++ programs. The core contributions of this thesis are outlined as follows:

- **WebAssembly Extension**: A minimal and generic extension to the WebAssembly instruction set, allowing for protected memory regions without code changes.

- **Compiler Toolchain:** A compiler toolchain that transparently transforms unmodified programs to provide spatial and temporal memory safety for stack and heap allocations.

- **Runtime:** A WASM runtime with support for our WebAssembly extension and modified WASM compiler that utilizes ARM's MTE.

- **Bounds Checks with MTE**: An implementation to eliminate expensive software-based bounds checks for 64-bit WASM programs.

**Evaluation on real hardware:** Evaluation of our implementation on ARM hardware, including performance and memory overheads as well as security guarantees, and MTE as implemented in actual production hardware.

# 2. Background

In this chapter we discuss the necessary background on which our work builds upon. We start by discussing WASM, memory safety in the context of WASM and ARM's PAC and MTE hardware extensions.

# 2.1. WebAssembly

WebAssembly [10], initially designed as an alternative, high-performance compilation target to JavaScript, continues to be applied in various use cases. WASM was carefully designed to allow compilation from high-performance languages traditionally compiled to native machine code such as C, C++, or Rust and for compilation to different native architectures.

Linear memory: WASM provides a linear memory that can be accessed by 32 or 64-bit integers. This allows the compilers and languages to manage memory without being forced into an unnatural idiom. Languages may ship their allocators, garbage collectors, and layout data structures as efficiently as possible. This linear memory can then be mapped directly to the virtual memory on the host.

**Structured control flow:** In WASM, unstructured control flow is not allowed by design. WASM uses indices into type- and bounds-checked tables instead of raw function pointers to make indirect function calls. For jumps, WASM provides a set of well-defined control flow constructs. This reduces the attack surface of programs compiled to WASM and aids code generation.

**Stack machine**: Since compilation targets offer different sets of registers, WASM does not expose registers but operates on a typed stack instead. The stack can be verified to be well-typed and compiled to diverse targets, such as register machines or intermediate representations (IRs) in a single pass. No assumptions about the number of guest registers are made, as these can vary between different architectures and runtimes, as they might reserve some registers for their own use (e.g., dedicating a register to hold some global state).

**Limited datatypes:** WASM defines four basic data types: 32 and 64-bit integer and floating-point types. Different proposals add vector-, garbage-collected-, and

reference types covering other use cases. There is no distinction between pointerand integer types. While this loses information present in the original program, such as pointer provenance, and prevents some optimizations, this is not considered a problem. In most cases, WASM is generated by an optimizing compiler, which has already performed optimizations relying on analyses such as alias analysis. The design of WASM allows for an efficient compilation to this format, which requires little optimization for the runtime compiling to native code.

Since its inception, WebAssembly has expanded its utility beyond the initial design goal to various other domains, such as Function as a Service (FaaS) workloads, as an alternative to Linux containers in Docker<sup>1</sup>, or as an isolation mechanism to enable running untrusted code within native applications, among other uses.

## 2.1.1. WebAssembly Sandbox

When accessing memory, the WASM runtime must ensure the access is within the bounds of the accessible linear memory. Then, the memory access is performed relative to the memory's base address. In current runtimes, this is usually achieved using two major approaches.

**Explicit bounds checks:** An explicit bounds check is inserted before each memory access, comparing the index with the bound of the current memory.

**Guard pages**: When running 32-bit WASM on 64-bit hosts, the runtime can leverage the fact that virtual memory is abundant. For each linear memory, 2<sup>32</sup> bytes, or 4GiB of virtual memory are allocated, with the memory beyond the guard being marked as inaccessible. The Memory Management Unit (MMU) will catch accesses into these pages, and the operating system will deliver a segmentation fault to the runtime, which will deliver a trap to the WASM program.

While the design of WebAssembly is designed to prevent malicious or erroneous programs from compromising the host, buggy programs are still vulnerable to classical memory safety errors discussed in section 2.2, such as buffer overflows.

# 2.2. Memory Safety in the context of WebAssembly

Programs written in languages like C or C++ are prone to memory safety bugs such as memory accesses to (1) out-of-bounds or (2) dangling pointers, which are the fundamental attack primitives enabling a whole class of attacks on a vulnerable or

<sup>1</sup>https://docs.docker.com/desktop/wasm/

buggy program [31]. Approaches to tackle these issues exist in several forms. Several studies have shown that in large software projects, memory safety bugs make up between 70 % and 75 % of all issues [15, 33, 34].

Lehmann et al. show that while some attack surfaces, such as those jumping to arbitrary addresses or injecting shellcode, are mitigated by the design of WebAssembly, buffer overflows or dangling pointer accesses are still possible [14]. Since WebAssembly does not provide separate read-only memory regions, this opens up other surfaces, allowing attackers to overwrite static data since compilers place them in the linear memory with both read and write permissions. Crucially, neither fundamental attack primitives (1) nor (2) are prevented by WebAssembly and can form the basis of an exploit.

Programs may be written in managed languages that prevent these attacks by not providing raw pointer accesses, such as Java, Python, JavaScript, or others. In these languages, memory access is performed through bounds-checked arrays or managed objects, such as classes. A garbage collector is responsible for cleaning up dangling objects. This results in all references pointing to valid objects and all memory accesses being bounds-checked. Other languages, such as Rust, take a different approach. In Safe Rust, the type system forbids many invalid programs, e.g., programs containing dangling references or raw pointer accesses. An escape hatch in the form of unsafe exists, which allows dropping down to the level of C and directly manipulating raw bytes. Both these approaches represent a fundamental tradeoff. Managed memory, either in the form of reference counting or through a garbage collector, incurs an overhead that may or may not be tolerated in some environments.

### 2.2.1. Software-Based Mitigations

To detect and mitigate memory safety bugs in languages that do not provide safety guarantees at the language level, numerous approaches have been proposed [28, 29, 20, 30]. Checks can be inserted automatically at the compiler level, an approach chosen by Address Sanitizer (ASan) and Hardware-Assisted Address Sanitizer (HWASan) [28, 30]. ASan incurs significant overhead, on average 73%, which is too high to be deployed in production and is usually only tolerated while testing or fuzzing software. A sampling-based version of ASan, GWP-Asan, is deployed in production in several large projects, which results in a low overhead but does not provide complete protection for a single process [29]. On a large scale, however, this approach allows for discovering real-world bugs that may not be triggered by testing or fuzzing workloads.

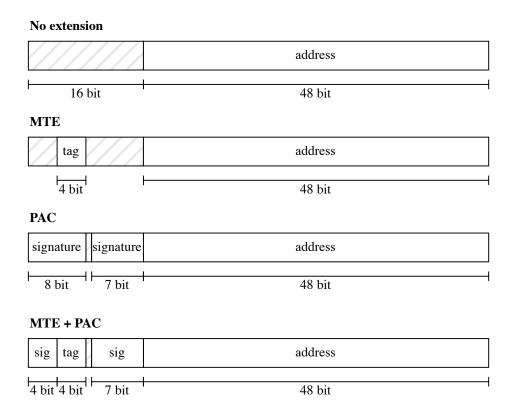

Figure 2.1.: Pointer layout on aarch64 in Linux with and without MTE and PAC enabled.

# 2.3. Memory Safety Hardware Extensions

As an alternative to flexible but slow software solutions to detect and prevent memory safety issues, CPU designers have developed several hardware extensions designed as an efficient foundation for memory safety. They provide security primitives that compilers or programmers can use to provide full or partial memory safety to programs while having a small enough additional memory footprint and performance overhead to ship these solutions in production.

In figure 2.1, we show the layout of pointer bits used for address translation in aarch64, the 64-bit variant of the ArmV8 instruction set [3], when running on Linux. Only 48 out of the available 64 bits are used to address memory, while the remaining bits are set to either 0 or 1 to differentiate between kernel and userspace addresses but are unused for further address translation. Hardware extensions such as Top Byte Ignore (TBI), MTE (section 2.3.1), or PAC (section 2.3.2) utilize those unused bits to store metadata.

# 2.3.1. Memory Tagging Extension (MTE)

ARMs MTE, available from ArmV8.5, provides a building block to prevent spatial and temporal memory safety violations [4]. MTE implements a lock-and-key mechanism where memory regions can be tagged with one of 16 distinct tags, and memory access is only allowed using pointers with the corresponding keys.

The locking mechanism is implemented by storing a 4-bit tag in bits 56–59 of an address (referred to as the logical tag). Accordingly, a tag is assigned to memory with a granularity of 16 bytes (referred to as the allocation tag).

On Linux, each process can configure MTE by switching between the following modes:

- **Disabled:** MTE is disabled, and no tag checks are performed.

- **Synchronous:** Tag mismatches cause a hardware fault on instruction retirement, and a segmentation fault is delivered to the application. The faulting instruction cannot read the affected memory location, or the update is not observable in the case of writes.

- Asynchronous: Tag mismatches do not cause an immediate hardware fault.

Instructions may be able to read the memory location regardless of tag mismatches, or the update may be observable in the case of writes. The fault is delivered after the instruction has retired in the form of a CPU flag. The kernel will check this flag at the next context switch and deliver a segmentation fault to the application.

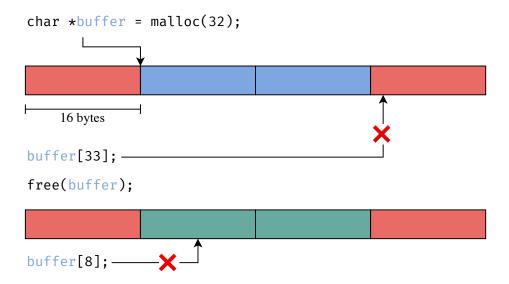

### Temporal and Spatial Memory Safety

MTE can provide spatial memory safety by assigning different tags to adjacent regions and temporal memory safety by retagging freed memory. An example can be seen in figure 2.2.

### 2.3.2. Pointer Authentication (PAC)

PAC [25] introduces primitives to prevent attackers from modifying pointers stored in memory. The extension provides three instructions for signing pointers, authenticating, or stripping the signature from pointers. PAC places the signature in the upper 16 bits of pointers, with the exact layout dependent on the operating system, hardware, and other factors, such as if MTE is enabled. The signature can be between 7 and 16 bits long.

Signed pointers are invalid and cannot be used to address memory. They are created using the pac\* instructions. Before being used, the signature needs to be removed. This

happens either with the aut\* instructions, which remove the signature if it is valid or produce a pointer that will trap when used if the signature does not match the address. The extension provides strip instructions to remove the signature regardless of whether it is valid or not.

MTE and PAC can be combined at the cost of bits available for the PAC signature. The exact layout of the PAC signature varies depending on the system. On Linux, bits 56–59 are used for MTE while bits 63–60 and 54–49 are used for PAC (see figure 2.1). The remaining bit 55 differentiates between lower and upper (kernel- and userspace) addresses.

# 3. Motivation

While WebAssembly provides strong safety and security guarantees, as discussed in section 2.1, they mainly guarantee safety for the host, but not for the program itself. In [14], Lehmann et al. show that while some attack surfaces, such as those injecting shellcode or jumping to arbitrary addresses, are mitigated by the design of WebAssembly, others, such as buffer overflows or write accesses to static, read-only data is possible and being used to exploit programs running in the wild. Such cases need to be mitigated at the language level by rewriting software in a safe language such as Rust, manually inserting bounds checks, which is error-prone, or inserting checks using the compiler and sanitizing the code.

Additionally, bugs like CVE-2023-4863 [7] continue to be exploited, showing that memory safety is not a solved problem. While they do not escape the WebAssembly sandbox, they pose a security risk to the programs themselves. In C, the use of unsafe primitives or bugs, such as missing bounds checks, can be exploited by the attackers, e.g., by overwriting a variable to elevate their privileges. In listing 1, the lack of bounds checks allows an attacker controlling the variable input to write beyond the allocation of buf and overwrite str.

```

void foo(char *input) {

char buf[32];

const char str = "Hello, World!";

strcpy(buf, input);

}

```

Listing 1: Vulnerable overflow.

WASM engines use various techniques to protect their sandboxes against malicious code (see section 2.1.1). While virtual memory and guard pages are preferred for performance, some situations (e.g., running 64-bit WASM) require software-based bounds checks. This approach provides necessary security but comes at a performance cost. In our measurements, switching to 64-bit WASM resulted in a roughly 6–8% overhead on out-of-order CPUs, which can speculate bounds checks, and 47% overhead on in-order CPUs (see detailed evaluation in section 7.2). The fallback to software-based bounds checks is thus especially painful when running on low-power in-order cores

using 64-bit WASM or in environments without an operating system, such as embedded devices. The results on the out-of-order CPUs are similar to a previous evaluation done by Szewczyk et al. [32].

# 4. Overview

In this thesis, we present a design for an extension that adds memory safety in WASM built on top of the WASM 64-bit memory proposal<sup>1</sup>. The extension is created to be minimally invasive and implementable using various techniques, including hardware extensions such as MTE or PAC, capability-based architectures like Capability Hardware Enhanced RISC Instructions (CHERI) [38], or software-based solutions similar to ASan [28] or HWASan [30] (see chapter 5).

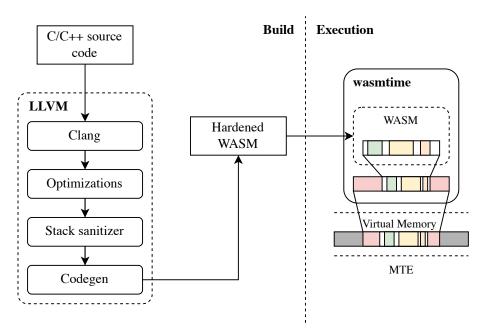

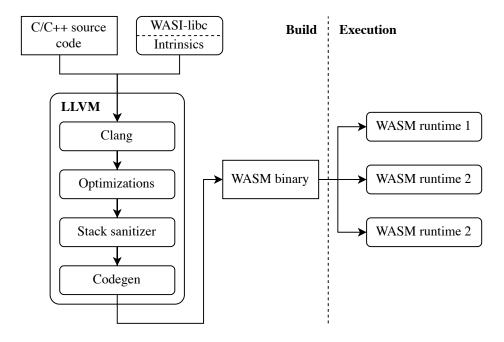

Figure 4.1.: Overview of the prototype implemented in this thesis.

In figure 4.1, we present our prototype of this design. Unmodified C/C++ source code is compiled using LLVM [13], where we implement a sanitizer that identifies and hardens stack allocations, along with a modified standard library based on WebAssembly System Interface (WASI) that protects heap allocations. LLVM then generates hardened

<sup>1</sup>https://github.com/WebAssembly/memory64

WASM binaries that can be run in wasmtime<sup>2</sup>. We modify wasmtime to process our WASM extension and implement it using MTE.

Additionally, we explore and implement a technique to efficiently sandbox WASM programs using MTE, eliminating expensive software-based bounds checks required for 64-bit WASM programs. This technique can be combined with the MTE-based memory safety implementation.

We analyze and benchmark various aspects of our implementation, including 32-bit and 64-bit WASM, and the MTE implementation on real hardware (see chapter 7).

<sup>&</sup>lt;sup>2</sup>https://wasmtime.dev/

# 5. Design

This chapter defines our threat model, WASM extension, and design to provide memory safety for programs compiled to WASM.

# 5.1. Threat Model

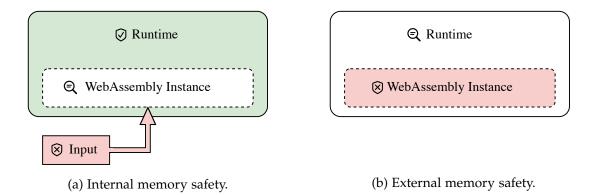

In our threat model (figure 5.1), we differentiate between two aspects of memory safety. In both models, we depict trusted components (marked with a  $\boxtimes$ ) in green and untrusted components (marked with a  $\boxtimes$ ) in red. We additionally highlight the component we are trying to harden (marked with a  $\boxtimes$ ).

Internal Memory Safety: Ensures memory safety within the boundaries of a sandbox. Our point of view is from within a WebAssembly instance, we trust the runtime (and the host we are running on), but we do not trust external input (figure 5.1a).

**External Memory Safety:** Maintains the memory safety of the sandbox itself against potentially malicious programs. Our point of view is from the runtime; we trust the platform we are running on, but not the WebAssembly programs we are executing (figure 5.1b).

Figure 5.1.: Threat model for internal and external memory safety.

# 5.1.1. Internal Memory Safety

For internal memory safety, the program within the sandbox and its runtime, including its compiler, are considered trusted and assumed to be bug-free. Untrusted input (e.g., network data, file reads) originates from outside the sandbox and may be controlled by an attacker. This model mirrors the threat environment of a standard non-WASM program. Potential threats include:

- **Buffer overflows:** Attempts to access memory beyond allocated buffer boundaries.

- Use-after-free: Attempts to access deallocated memory.

As discussed in section 2.1, WebAssembly's design inherently mitigates some threats common in non-WASM environments, so we will not consider the following vectors:

- **Return-oriented attacks:** WASM's structured control flow constructs prevent arbitrary code execution through stack manipulation.

- **Calling unknown function pointers:** Function tables enforce a strict mechanism for function calls, ensuring the integrity of call targets.

## 5.1.2. External Memory Safety

For external memory safety, we focus on the security of the sandbox. Threats originate from running untrusted programs, which may be adversarial or buggy.

- **Sandbox escapes:** Attempts to break out of the sandbox's restrictions and access host resources.

- **Side-channel attacks:** Exploiting timing differences or resource usage patterns to infer sensitive information.

We assume that the operating system and underlying target architecture are free of bugs that malicious targets might exploit. This does not include assumptions about potential spectre-like [12] attacks. The compiler needs to ensure that bounds checks are guarded against side-channel attacks.

Additionally, we do not consider exploits of the program running in the sandbox as vulnerabilities as long as they stay contained in the sandbox.

Figure 5.2.: Overview of the compilation and execution workflow.

### 5.2. Overview

Figure 5.2 presents an overview of our prototype. At build time, the unmodified C/C++ sources and a modified version of libc are compiled using LLVM [13]. After optimizations, a stack sanitizer analyzes all functions and inserts instrumentation as necessary. LLVM's backend then generates WebAssembly binaries that can be deployed and executed on various devices.

# 5.3. WebAssembly Extension

We designed an extension to WebAssembly that provides primitives to the modified standard library and the stack sanitizer to guarantee memory safety for selected allocations. Our extension builds on wasm64, the 64-bit variant of WebAssembly. We choose wasm64, because it uses a 64-bit integer index type, with 48 of those bits used to index memory. This allows us to allocate and store up to 16 bits of metadata per pointer.

For our extension, we propose the notion of abstract segments and tagged pointers. We introduce three new instructions that allow the creation of abstract segments and

tagged pointers from raw pointers. These pointers carry provenance and can only access the segment they were created with. Conversely, segments can only be accessed by the tagged pointer created with them rather than with raw indices without provenance. We introduce the following new instructions. Each instruction takes a constant unsigned offset o, which allows compilers to fold in constant offsets when manipulating segments.

(new instructions) e :=**segment.new**  $o \mid$ **segment.set\_tag**  $o \mid$ **segment.free**  $o \mid$

In the following paragraph, we describe the new instructions in detail.

- segment.new: Create a new, zeroed memory segment. This instruction takes two arguments: a memory index and a size. The instruction generates a new tag, assigns it to the piece of memory, and returns a tagged pointer that can be used to access the segment.

- segment.set\_tag: This instruction takes a memory index, a length, and a tagged pointer and applies the tag from the tagged pointer to the memory segment located at the index with the passed length. This can be used to move ownership from one segment to another or to merge segments.

- segment.free: This instruction invalidates a segment by tagging the segment with a new, implementation-defined tag. This instruction takes two arguments: a memory index and a length. After this instruction, the tagged pointer being used to access the segment is no longer valid, and accessing the segment through it will result in a trap.

We also modify the semantics of existing load and store instructions. They still take an integer as an index, but we introduce provenance to integers, which we can track at runtime using the unused 16 upper bits in pointers. If a segment is accessed, the runtime will check that the tagged pointer is allowed to access the segment, i.e., the metadata matches the metadata created by the segment.new instruction. If this is not the case, the runtime throws a trap.

At startup, the linear memory consists of a single segment that can be accessed using untagged indices, allowing unmodified code to run under our new semantics without modifications. This design choice also allows the gradual integration of safety primitives into specific parts of WebAssembly applications where enhanced security is required. For instance, it enables the introduction of a hardened malloc implementation, which prevents spatial and temporal safety bugs for heap-allocated memory. Additionally, we can analyze stack allocations to only harden those accessed using untrusted indices or escape our analysis, e.g., by taking their address and passing it to another function.

$$C_{\text{memory}} = n$$

$$C \vdash \mathbf{segment.new} \ o : \mathbf{i64} \ \mathbf{i64} \to \mathbf{i64}$$

$$C_{\text{memory}} = n$$

$$C \vdash \mathbf{segment.set\_tag} \ o : \mathbf{i64} \ \mathbf{i64} \to \epsilon$$

$$C_{\text{memory}} = n$$

$$C \vdash \mathbf{segment.free} \ o : \mathbf{i64} \ \mathbf{i64} \to \epsilon$$

Figure 5.3.: Typing rules of the new instructions. For the definition of context *C*, see the WASM paper [10].

**Alignment** All segments are aligned to 16 bytes, corresponding to the alignment of MTE (see section 2.3.1). This is an implementation choice that may be changed once we support additional implementations. More details can be found in section 9.1.

# 5.3.1. Typing Rules

In figure 5.3, we extend the typing rules of the WASM paper [10] in the notation of Pierce [22]. The rules are of the form of  $C \vdash e : tf$ . An instruction e is valid under the context e, with e is used to access a context component, such as the memory. The rule e is the ensures that the instruction can only be used when a memory is declared. The type e is the expect of the expect of the instruction manipulates the operand stack. The instruction e expects an operand stack where it pops off e and pushes e in the expect of the e

$$(store) \ s \coloneqq \{\dots, tag \ taginst^*\}$$

$$taginst \coloneqq b^*$$

$$s; (\mathbf{i64.const} \ k); (t.\mathbf{load} \ a \ o) \hookrightarrow_i \ trap \qquad (5.1)$$

$$if \ s_{tag}(i,k+o,|t|) \neq tag(k)$$

$$s; (\mathbf{i64.const} \ k); (t.\mathbf{const} \ c); (t.\mathbf{store} \ a \ o) \hookrightarrow_i \ trap \qquad (5.2)$$

$$if \ s_{tag}(i,k+o,|t|) \neq tag(k)$$

$$s; (\mathbf{i64.const} \ k); (\mathbf{i64.const} \ l); (\mathbf{segment.new} \ o) \hookrightarrow_i \ s'; (\mathbf{i64.const} \ t) \qquad (5.3)$$

$$if \ t = \text{new\_tag}(k+o) \land s' = s \ \text{with} \ s_{tag}(i,k+o,l) = t$$

$$s; (\mathbf{i64.const} \ k); (\mathbf{i64.const} \ l); (\mathbf{segment.set\_tag} \ o) \hookrightarrow_i \ s' \qquad (5.4)$$

$$if \ s' = s \ \text{with} \ s_{tag}(i,k+o,l) = t$$

$$s; (\mathbf{i64.const} \ k); (\mathbf{i64.const} \ l); (\mathbf{segment.free} \ o) \hookrightarrow_i \ s' \qquad (5.5)$$

$$if \ t = \text{free\_tag}(k+o) \land s' = s \ \text{with} \ s_{tag}(i,k+o,l) = t$$

$$s; (\mathbf{i64.const} \ k); (\mathbf{i64.const} \ l); (\mathbf{segment.new} \ o) \hookrightarrow_i \ trap \qquad (5.6)$$

$$otherwise$$

$$s; (\mathbf{i64.const} \ k); (\mathbf{i64.const} \ l); (\mathbf{segment.set\_tag} \ o) \hookrightarrow_i \ trap \qquad (5.7)$$

$$otherwise$$

$$s; (\mathbf{i64.const} \ k); (\mathbf{i64.const} \ l); (\mathbf{segment.free} \ o) \hookrightarrow_i \ trap \qquad (5.8)$$

$$otherwise$$

Figure 5.4.: Small-step reduction rules of the new instructions and added rules for load/stores. See the WASM paper [10] for the definitions of all rules and auxiliary constructs.

### 5.3.2. Small-Step Reduction Rules

In figure 5.4, we extend the small-step reduction rules from the WASM paper [10] using the notation established by Plotkin [23]. The lower portion of figure 5.4 presents new tag-aware load/store rules that take precedence over the existing ones and new rules for the introduced instructions.

To signal a trap, we reuse operators from the original WASM rules, including the

**trap** operator. The state, s, is augmented with a storage mechanism that assigns a tag t, to each 16-byte granule of memory. We use the following notation:

- $t = s_{tag}(i, addr, len)$ : Extracts the tag t for a memory region in instance i accessed at address addr with length len, if the tag is the same for all bytes in the range [addr, addr + len).

- s' = s with tag(i, addr, len) = t: Updates the state with new tags for the memory region at address *addr* with length *len*, if *addr* is aligned to 16 bytes, i.e. *addr* mod 16 = 0

- t = tag(pointer): Extracts the tag from a tagged pointer.

- $t' = \text{new\_tag}(t)$ : Creates a tagged pointer t' from an untagged pointer t to be used for a new segment. The tag is randomly chosen from a pool of tags.

- $t' = \text{free\_tag}(t)$ : Creates a tagged pointer t' for the purpose of freeing a segment. The tag is different from the tag stored in t.

Figure 5.4 highlights the added and modified components in the rules. The added load/store rules, specified in equations (5.1) and (5.2), enforce trapping on tag mismatches. Similarly, when an access spans memory regions with different tags, these rules trap. The rules for executing the new instructions, which modify the state by setting tags, are presented in equations (5.3) to (5.8). Equations (5.3) to (5.5) represent the default case where tags are assigned to aligned, in-bounds addresses, with equations (5.6) to (5.8) representing the cases with unaligned or out-of-bounds accesses. Each reduction rule is depicted with the operand stack's top and state s on the left-hand side, representing the pre-execution state, and the resulting stack and state after the execution of the instruction on the right-hand side. For the rules with  $\hookrightarrow_i$ , the i represents the instance the instruction is executed in.

# 5.3.3. Example

We will demonstrate our WASM extension using the C snippet in listing 2, which allocates 64 bytes on the stack.

This requires the compiler to instrument the stack allocation, create a new segment, and free the segment before returning to the caller, i.e., giving ownership of the stack slot back to the stack frame, as demonstrated in listing 3.

The compiler allocates the slot for buf on the stack, decrementing the global \$\_\_stack\_pointer acting as the stack pointer (lines 2 to 5). Then, a new segment of size 64 is created, and the tagged pointer to it is stored in the local \$buf (lines 8 to 10).

```

void foo() {

char buf[64];

// ...

return;

}

```

Listing 2: Example of a C program allocating 64 bytes on the stack.

```

_{1};; Allocate space on the stack

2 global.get $__stack_pointer

3 i64.const 64

4 i64.sub

5 global.tee $__stack_pointer

7;; create a segment

8 i64.const 64

9 segment.new

10 local.set $buf

11

12;; ...

14;; retag with stack pointer tag

15 local.get $buf

16 global.get $__stack_pointer

17 i64.const 64

18 segment.set_tag

20;; reset stack pointer

21 global.get $__stack_pointer

22 i64.const 64

23 i64.sub

24 global.set $__stack_pointer

```

Listing 3: Generated WASM for code from listing 2.

Before returning, the segment is retagged using the stack pointers tag, i.e., restoring the previous tag and allowing access through the stack pointer (lines 15 to 18). Then, the stack pointer is reset, freeing the stack frame (lines 21 to 24).

# 5.3.4. Heap Safety

The memory allocator needs to be aware of segments to provide heap safety. When allocating memory, it aligns the requested size to 16 bytes, creates a segment, and returns the corresponding tagged pointer. This prevents overflows from corrupting allocator metadata or other memory segments. A modified allocator implementation looks conceptually similar to the snippet in listing 4.

```

void *malloc(size_t length) {

void *chunk = /* perform allocation */;

return __builtin_wasm_segment_new(chunk, length);

4}

```

Listing 4: Example of a malloc implementation utilizing the memory safety extension.

When compiled to WASM, we see just three new instructions added to the generated code in listing 5 (lines 6 to 8). This proves that our extension is minimally invasive, as the calling code does not need to be changed and will continue to work as-is. Similarly, when freeing or reallocating memory, the allocator needs to ensure that the no longer valid memory is retagged.

```

(func $malloc (param $length i64) (result i64) (local $chunk)

;; perform allocation and place the result in $chunk

;; create a segment

local.get $chunk

local.get $length

segment.new

;; implicit return

```

Listing 5: Generated WASM for code from listing 4.

Figure 5.5.: Algorithm to detect and harden safe and unsafe stack allocations.

# 5.3.5. Stack Safety

For stack safety, we create segments from stack slots when entering a function. Before returning, all stack slots are untagged and reassigned to the stack frame. This allows other functions to use the memory and prevents stack slots from being accessed after returning from a function.

However, only some stack allocations need to be turned into segments. We can omit allocations that do not escape or are only accessed using statically verifiable indices. Creating segments for these would result in excessive runtime and memory overhead, as each allocation would need to be aligned to 16 bytes and processed when entering and returning from a function.

To address this, we design an algorithm (figure 5.5) that identifies safe memory regions within the stack which do not require protection, thus avoiding creating segments for the slots mentioned above. In figure 5.5, we present a simplified version of our algorithm. We iterate over all stack allocations and check if the allocation (a) escapes the function or (b) is indexed into using an unsafe getelementptr (GEP) instruction.

### **5.3.6.** Example

We demonstrate the algorithm using the functions in listing 6. In the code example, i (line 2) is safe, as its address is not used in a potentially unsafe address computation and does not escape. The variables bytes\_read and buf (lines 3 and 4) are deemed unsafe as their address escapes (line 5). Additionally, buf is accessed using an untrusted index (line 6).

In function bar, buf also needs to be instrumented as it escapes: the pointer to it

```

char foo(int index) {

int i = 0; // safe

int bytes_read = 0; // unsafe

char buf[32]; // unsafe

read_input(buf, &bytes_read);

return buf[index];

}

char *bar() {

char buf[32]; // unsafe

return buf;

}

```

Listing 6: Example code for safe and unsafe stack slots.

is returned to the caller (line 11). Any attempt to dereference the value returned by bar is undefined behavior and will be caught by our instrumentation, preventing difficult-to-debug bugs or potential vulnerabilities.

This algorithm effectively balances the need for stack safety with performance and memory efficiency constraints.

# 6. Implementation

We implement our prototype in the LLVM framework, wasi-libc, and the wasmtime WebAssembly runtime. The following sections detail the specific modifications and extensions to each component and some implementation choices and details to tackle specific problems.

# 6.1. LLVM

We choose LLVM as our compiler, from C/C++ to WebAssembly. We modify the existing WASM backend and add support for the extension described in section 5.3, allowing LLVM to emit the new instructions.

### 6.1.1. LIVM IR

In the middle end, we introduce three new intrinsic functions that correspond and are lowered to our WASM instructions by the backend.

```

ptr @llvm.wasm.segment.new(ptr, i64)

```

Takes an untagged pointer and a size, creates a new segment and returns the tagged pointer to it.

```

void @llvm.wasm.segment.set_tag(ptr, ptr, i64)

```

Takes a pointer to a memory region we want to retag, a pointer containing the new tag, and a size, and sets the tag for the memory segment.

```

void @llvm.wasm.segment.free(ptr, i64)

```

Takes a tagged pointer and a size and assigns a new tag to the region, ensuring the tagged pointer cannot be used to access it anymore.

The clang front end or a sanitizer pass can insert calls to these intrinsic functions. Listing 7 shows how we lower a function that allocates 32 bytes on the stack to LLVM IR

Listing 7: Code generated for a function that allocates 32 bytes on the stack.

Table 6.1.: Flags added to LLVM.

| Flag                      | Description                         | Required Flags |

|---------------------------|-------------------------------------|----------------|

| -mmem-safety              | Enable the memory safety extension. |                |

| -fsanitize=wasm-memsafety | Enable the stack sanitizer.         | -mmem-safety   |

### 6.1.2. LLVM Sanitizer Pass

In LLVM, we introduce a WASM-specific sanitizer pass that can be enabled via a compiler flag (see table 6.1), designed to provide memory safety for stack allocations when compiling to WebAssembly. This sanitizer analyzes functions for stack allocations, applies padding, and inserts calls to the intrinsics described in section 6.1.1 to create segments, as discussed in section 5.3.5. The pass runs after all optimizations, ensuring we do not block passes that might remove stack allocations, such as mem2reg.

For each hardened allocation, we insert a call to the segment.new intrinsic after the allocation and replace all uses of the pointer to the allocation with our tagged pointer. Before returns or tail calls, we need to return ownership of the segment to the stack frame, i.e. retagging using the stack pointers tag. This serves two purposes: (1) subsequent code is able to access the memory through the stack pointer without a tagged pointer, and (2) use-after-return errors are caught, as the tagged pointer is not able to access the segment.

### 6.1.3. C extension

To create and manipulate segments manually, e.g., to build a segment-aware memory allocator, we expose the memory safety features to C in the form of built-in functions

Table 6.2.: Flags added to wasmtime.

| Flag                 | Description                         | Required Flags     |

|----------------------|-------------------------------------|--------------------|

| -C mte               | Enable the use of MTE.              |                    |

| -C mte-bounds-checks | Use MTE for bounds checks.          | -C mte             |

| -W mem-safety        | Enable the memory safety extension. | -C mte -W memory64 |

that clang lowers to calls to the corresponding LLVM intrinsics.

```

void *__builtin_wasm_segment_new(void *, unsigned long);

void __builtin_wasm_segment_set_tag(void *, void *, unsigned long);

void __builtin_wasm_segment_free(void *, unsigned long);

```

The functions can be used as regular functions in C code, as illustrated in listing 8.

```

void *my_malloc(unsigned long size) {

void *memory = malloc(size);

return __builtin_wasm_segment_new(memory, size);

}

```

Listing 8: Example of how a built-in function can be called from C.

### 6.2. WASI Libc Modifications

To allow us to run applications relying on libc on wasm64, we port the WebAssembly System Interface (WASI) and wasi-libc to wasm64. This work includes changing size and pointer types from 32 to 64 bits.

We modify dlmalloc, the default allocator in wasi-libc, to provide memory safety for heap allocations. We insert calls to the built-in functions exposed to C as necessary, creating memory segments and returning tagged pointers to these segments. This protects both allocator metadata and adjacent allocations from being accessed or modified through heap overflows. When freeing or reallocating memory, segments are freed, ensuring temporal safety.

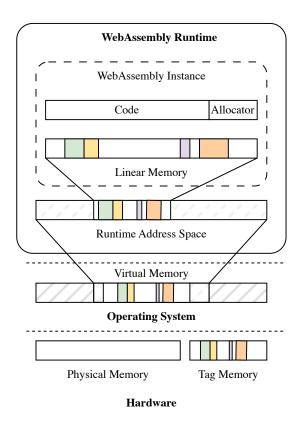

Figure 6.1.: The memory safety extension, as implemented in wasmtime using MTE. Memory segments are tagged, with different colors representing different tags. The processes virtual memory maps to physical memory and tag memory, which stores the tags assigned to memory granules.

# 6.3. Internal Memory Safety

We implement our prototype in wasmtime<sup>1</sup>, a WebAssembly runtime mainly focusing on speed and correctness, written in Rust. Wasmtime features an optimizing compiler, cranelift<sup>2</sup>, and its own IR, namely Cranelift IR (CLIF).

In figure 6.1, we present an overview of our implementation of the memory safety extension in wasmtime using MTE. We modify wasmtime and its supporting libraries and extend it with support to parse and process the memory safety extension described in section 5.3. We add support for MTE in the form of new instructions and lowering rules to cranelift, allowing wasmtime to generate MTE instructions when compiling

<sup>1</sup>https://wasmtime.dev/

<sup>&</sup>lt;sup>2</sup>https://cranelift.dev/

Table 6.3.: Default tag t for the linear memory.

| <b>Memory Safety</b> | MTE Sandboxing | Default Tag                            |

|----------------------|----------------|----------------------------------------|

| No                   | No             | $t \in \{0\}$                          |

| No                   | Yes            | $t \in \{1, \ldots, 15\}$              |

| Yes                  | No             | $t \in \{1, \dots, 15\}$ $t \in \{0\}$ |

| Yes                  | Yes            | $t \in \{1\}$                          |

for a target that supports them. We run in MTE synchronous mode to catch and stop memory safety violations before their effects become observable to the violating or any other process. These features can be enabled using the flags described in table 6.2.

The memory is tagged by default with one of the tags described in table 6.3, depending on the configuration. This tag is then stored in the heap base pointer of the WASM instance, allowing memory accesses through the pointer.

For MTE, we store the logical tag in the upper, unused bits of the WASM index. This index becomes a valid pointer once it is translated to an address by adding it to the heap base address.

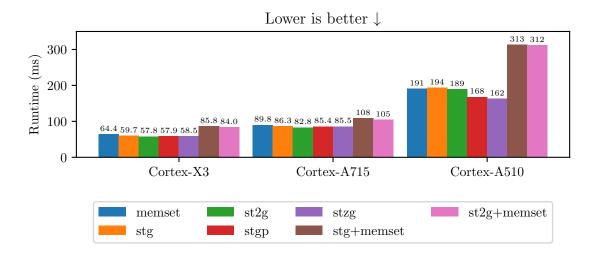

#### 6.3.1. Tagging Memory

When setting an allocation tag, we have four choices:

- 1. stg: Setting the tag for a single tag granule,

- 2. st2g: Setting the tag for two tag granules,

- 3. stzg: Setting the tag for a single granule and zeroing the granule.

- 4. stgp: Setting the tag for a single granule and storing a pair of registers.

To ensure new segments are always zeroed, options (1) and (2) require an additional memset. Our benchmarks for all four variants (see section 7.5) show stzg as the variant with the lowest overhead while also clobbering one less register compared to stgp.

#### 6.3.2. Lowering WASM to machine code

In the following paragraphs, we describe how we lower each of our instructions to an MTE backend.

segment.new: To create a new segment, we (1) check that the requested segment is inside the linear memory of the guest, (2) generate a random logical tag and insert it into the index, and (3) set the allocation tag for the segment. This involves generating a loop that iterates over the size of the segment and setting the tag using stzg, which also zeroes the memory.

segment.set\_tag : To change ownership of a segment, we (1) check that the requested segment is inside the linear memory of the guest and (2) set the new allocation tag for the segment. Here, we do not need to create a new, random tag, as we have passed a predefined tag.

segment.free : To invalidate a segment, we (1) check that the requested segment is inside the linear memory of the guest and (2) set the default allocation tag for the segment. The default tag depends on the configuration and can be taken from table 6.3.

We implement several optimizations to ensure our generated code runs efficiently. When setting the allocation tag for a segment, we generate a loop iterating over the size of the segment. If the size of the loop is known at compile time, we unroll the loop to tag up to 160 bytes per iteration to avoid branch instructions. We choose this tradeoff between code size and reducing the number of branch instructions executed.

#### 6.3.3. Migration of the Linear Memory

When resizing linear memory, the runtime must relocate the existing contents and the MTE tags if active. We have two primary migration strategies (see figure 6.2).

**Temporarily disable MTE**: Disable MTE globally, copy memory and tags, then reenable MTE. This compromises memory safety during the migration for other threads in the same process relying on MTE and can thus only be used if only a single WASM instance is running.

**Copy data and tags**: Load the memory tag for each 16 byte granule. Use the tag to safely load and store data between memory regions, then set the tag for the new granule.

We have measured the performance of both approaches in section 7.5.4. After taking the performance difference into consideration, we chose the second approach, as the approach to temporarily disable MTE relies on only a single thread in the process requiring MTE and is only marginally faster on some CPUs and slower on others.

```

1 disable_mte();

2 memcpy(from, to, len);

3 while from != end {

4   asm!(

5    "ldg {tag}, [{from}]",

6    "stg {tag}, [{to}], #16",

7    tag = out(reg),

8    from = in(reg) from,

9    to = inout(reg) to,

10  );

11  from = from.add(16);

12 }

13 enable_mte();

```

```

while from != end {

asm!(

"ldg {from}, [{from}]",

"ldg {to}, [{from}]",

"stgp {val1}, {val2}, [{from}]",

from = in(reg) from,

to = inout(reg) to,

val1 = out(reg) _,

val2 = out(reg) _,

);

from = from.add(16);

}

```

- (a) Code generated for the first migration approach.

- (b) Code generated for the second migration approach.

Figure 6.2.: Variants on how to migrate tagged memory.

## 6.4. External Memory Safety

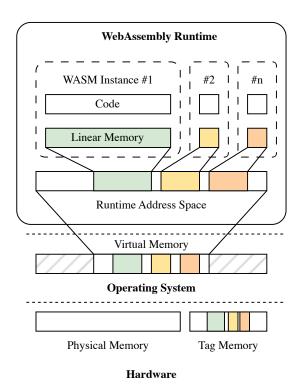

In figure 6.3, we show our approach to utilize memory tagging to replace software-based bounds checks while preserving external memory safety. The runtime assigns a tag (see table 6.3) to each instance on module instantiation. This tag is stored in the heap base address. Memory access translation then involves adding the accessed index to the tagged heap base address. The memory outside the linear memory, i.e., memory belonging to the runtime, is always tagged with the zero tag, ensuring MTE catches accesses outside the sandbox with minimal modifications to the runtime.

However, we face a limitation in the number of sandboxes for this approach. Since MTE only offers up to 16 distinct tags, we are limited to up to 15 different sandboxes within one process, as we need to reserve one tag for the runtime.

We can combine this approach with the memory safety extension (see section 6.3) by further restricting the number of sandboxes in one process and thus freeing up tag bits for the memory safety extension. While it would be possible to assign up to three MTE tag bits for sandboxing, we allocate three bits for the memory safety extension, thus just allowing a single instance to run in the same process. We designate the lowest tag bit to determine whether memory belongs to the runtime or the linear memory. Since we reserved the zero tag for the runtime, we tag the linear memory with the tag 1. The remaining three tag bits used for the memory safety features can be generated by segment.new. This results in memory indices always having an even logical tag, with the actual memory locations being assigned an odd allocation tag.

Figure 6.3.: Bounds checks as implemented in wasmtime using MTE. Each instances linear memory is assigned a unique tag, which re represent using different colors. The virtual memory of the process maps to physical memory and tag memory, which stores the tags assigned to memory granules.

This approach comes with the following challenges:

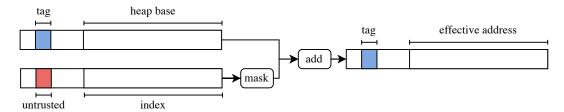

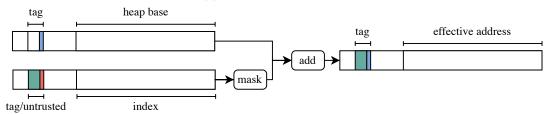

- 1. Adding a tagged user pointer to the heap base address should be performant and result in the correct tag for the respective memory.

- 2. Untrusted WASM modules should not be able to forge tags that allow them to access memory beyond their allocated sandbox.

As accesses are performed through integers, which can be arbitrarily changed by code, adding an untrusted index to the heap base can be exploited to arbitrarily set the resulting logical tag, potentially allowing code to escape the sandbox. To prevent this issue, we mask the tag bits allocated for the runtime from the index before address computation, as shown in figure 6.4. Figure 6.4a shows the masked bits when only MTE bounds checking is enabled. In this case, all tag bits are assigned for bounds checks and are masked out of the tag bits in the index. In figure 6.4b, we demonstrate what

MTE Sandboxing **Memory Safety** Tag Mask No Yes and 0xF0FF\_FFFF\_FFFF No

and OxFEFF\_FFFF\_FFFF

Table 6.4.: Tag mask for the index.

Yes

No

No

Yes

Yes

(a) MTE bounds checks.

(b) MTE bounds checks with memory safety extension.

Figure 6.4.: Effective address calculation with MTE bounds checks.

happens when both MTE bounds checking and memory safety are enabled. Here, only the lowest bit is assigned for bounds checks, while the remaining three are assigned to the memory safety extension. In table 6.4, we present the mask used for each configuration.

**Excluding Tags from Random Tag Generation** If we are running with MTE bounds checks enabled, we need to ensure that certain tags cannot be generated by instructions such as irg (insert random tag) or addg (add tag). Excluded tags can be either specified as an exclude mask via an immediate parameter or an include mask via a prctl call. We choose the latter option and set the include mask at startup time. In table 6.5, we list the include masks and included tags for the instructions mentioned above. If the memory safety extension is disabled, none of these instructions will be emitted, so we do not need to exclude tags from being generated.

Table 6.5.: Included tags for irg, addg instructions depending on configuration.

Memory Safety | MTE Sandboxing | Tag Include Mask | Included Tags

| Memory Safety | MTE Sandboxing | Tag Include Mask | Included Tags             |

|---------------|----------------|------------------|---------------------------|

| No            | No             | _                | _                         |

| No            | Yes            | _                | _                         |

| Yes           | No             | Oxffff           | $t \in \{1,2,\ldots,15\}$ |

| Yes           | Yes            |                  | $t \in \{2,4,\ldots,14\}$ |

# 7. Evaluation

## 7.1. Experimental Setup

We conduct our benchmarks on a Google Pixel 8 equipped with a Google Tensor G3 chip, including  $1 \times \text{Cortex-X3}$  (2.91 GHz),  $4 \times \text{Cortex-A715}$  (2.37 GHz), and  $4 \times \text{Cortex-A510}$  (1.7 GHz) cores, with MTE enabled. See table 7.1 for details on the benchmarked cores. As of the time of writing, this is the sole commercially available device featuring MTE. To mitigate thermal throttling, we attach a cooling fan to the device. Each performance test is run on each CPU type available on the Tensor G3 chip by pinning it to a single respective core. We run the benchmarks from the PolyBench/C 3.2 suite [24], which includes 30 kernels from domains such as linear algebra, data mining, stencils, and medley operations.

Table 7.1.: Comparison of the benchmarked cores.

| Spec               | Cortex-X3          | Cortex-A715       | Cortex-A510       |

|--------------------|--------------------|-------------------|-------------------|

| Cores              | 1                  | 4                 | 4                 |

| Pipeline           | out-of-order       | out-of-order      | in-order          |

| Superscalar        | Yes                | Yes               | Yes               |

| Architecture       | ArmV9.2            | ArmV9.2           | ArmV9.2           |

| Maxmimum Frequency | 2.91 GHz           | 2.37 GHz          | 1.7 GHz           |

| L1 I-Cache/D-Cache | 64 KiB             | 32/64 KiB         | 32/64 KiB         |

| L2 Cache           | 512 KiB – 1024 KiB | 128 KiB – 512 KiB | 128 KiB – 512 KiB |

| L3 Cache           | 512 KiB – 16 MiB   | 512 KiB – 32 Mib  | 256 KiB – 16 Mib  |

Table 7.2.: Runtime benchmarking configurations.

| Variant    | Pointer Width | Memory Safety | MTE Bounds Checks |

|------------|---------------|---------------|-------------------|

| wasm32     | 32-bit        | No            | No                |

| wasm64     | 64-bit        | No            | No                |

| mem-safety | 64-bit        | Yes           | No                |

| mte-bounds | 64-bit        | No            | Yes               |

| combined   | 64-bit        | Yes           | Yes               |

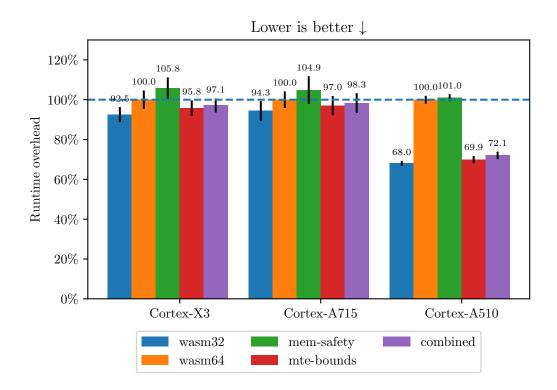

#### 7.2. Performance Overheads

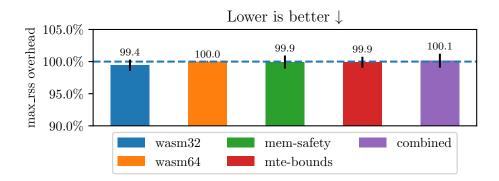

Figure 7.1.: PolyBench/C runtime overheads of different configurations described in table 7.2, normalized to wasm64.